低噪声亚采样锁相环的设计-电路图讲解-电子技术方案

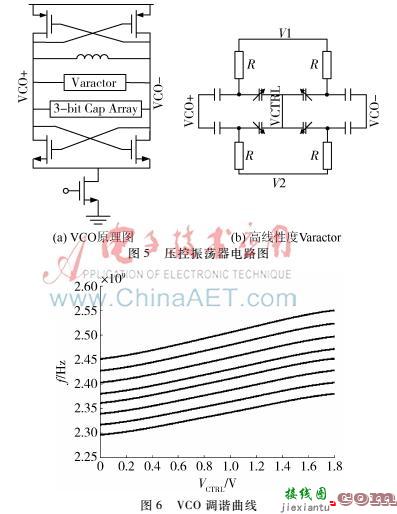

介绍了一种2.4 GHz的低噪声亚采样锁相环。环路锁定是利用亚采样鉴相器对压控振荡器的输出进行采样。不同于传统电荷泵锁相环,由于在锁定状态下没有分频器的作用,由鉴相器和电荷泵所产生的带内噪声不会被放大N2倍,从而会使锁相环的带内噪声极大程度地减小。在输出电压摆幅相同的情况下,压控振荡器采用NMOS、PMOS互补结构降低了锁相环的功耗。锁相环的设计在TSMC 180 nm CMOS工艺下完成,在1.8V的供电电压下,锁相环功耗为7.2 mW。在偏移载波频率200 kHz处,环路的带内噪声为-124 dBc/Hz。

0引言 在无线通信系统中,一个低抖动、低噪声的时钟信号是必不可少的。锁相环目前被广泛应用于产生高精度的时钟信号,例如为无线射频收发机系统提供稳定的本振时钟信号。低噪声的本振信号对于无线收发机系统的整体性能起着至关重要的作用。 在传统电荷泵锁相环中,由于分频器的作用,带内噪声性能会被很大程度恶化。通常情况下,会选取较小的环路带宽来抑制由鉴频鉴相器和电荷泵所带来的带内噪声。然而,减小环路带宽会增加锁相环的锁定时间以及芯片面积。 由于亚采样锁相环在锁定状态下没有分频器的作用,所以能很好地解决环路带宽与噪声之间的折中问题,既能获得大的环路带宽,又能减小锁相环的相位噪声。 本文分析了传统电荷泵锁相环的带内噪声,提出了低噪声亚采样锁相环,给出了电路各模块的具体实现和电路仿真结果。

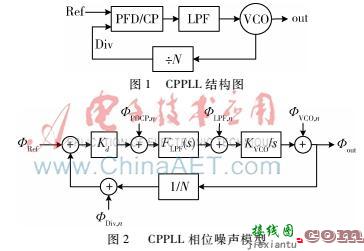

1传统电荷泵锁相环的带内噪声 图1为传统电荷泵锁相环(CPPLL)的基本结构,主要由鉴频鉴相器(Phase and Frequency Detector, PFD)、电荷泵(CP)、环路滤波器(Low Pass Filter, LPF)和压控振荡器(VCO)组成。图2所示为CPPLL的相位噪声模型,Kd为PFD/CP线性增益,FLPF(s)为环路滤波器的传输函数,KVCO/s为VCO的增益。

CPPLL带内噪声主要由PFD/CP的噪声贡献,利用图2的相位域模型,可以得到闭环PD/CP的噪声传输函数为:

HPDCP(s)=φout,nφPDCP,n=1Kd·G(s)1+G(s)/N(1)

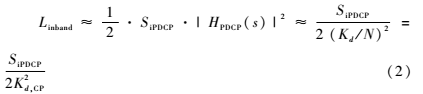

其中,G(s)= Kd·FLPF·KVCO/s是PLL开环传递函数。所以由PFD/CP贡献的带内噪声为:

其中,Kd=ICP/2π,相位噪声Linband通常表示为单边带噪声功率,SiPDCP是PFD/CP噪声频率谱密度。从式(2)可以看出,由于分频器的存在,PLL的带内噪声会被放大N2倍。从而较大的Kd,CP即较大的 PFD/CP线性增益Kd及较小的分频比N会得到更优的噪声性能。

其中,Kd=ICP/2π,相位噪声Linband通常表示为单边带噪声功率,SiPDCP是PFD/CP噪声频率谱密度。从式(2)可以看出,由于分频器的存在,PLL的带内噪声会被放大N2倍。从而较大的Kd,CP即较大的 PFD/CP线性增益Kd及较小的分频比N会得到更优的噪声性能。

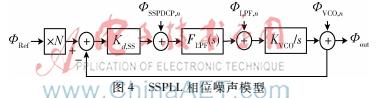

2SSPLL工作原理及噪声分析 本文提出的亚采样锁相环基本结构框图如图3所示,主要由核心的亚采样环路(Core Loop)及锁频环(FLL)构成。如果仅使用核心电路,由于SSPD的捕获范围有限,在采样的过程中,采样器无法区分被采样的频率是所需的N·fRef 还是fRef 的其他谐波,故加入FLL可以得到所需的锁定频率。SSPD采用参考信号Ref对VCO的输出进行采样。使用相同的SSPD/CP作为Dummy采样器,可以消除从采样开关到VCO的电荷注入和补偿BFSK效应[4],从而使采样PLL的参考杂散性能得到优化。

当环路未锁定时,核心采样电路与FLL一起工作,当Ref与FLL中分频器输出Div相位差小于π,PFD的输出会掉入死区(Deadzone),使得CP2无法开启,FLL停止工作,只有核心采样电路单独工作,直至锁定。当环路锁定时,Ref的上升沿与VCO差分输出波形的交叉点对齐。SSPD采样后,可以通过CP将采样的电压转化为上下电流IUP和IDN。因为Ref采样得到的电压相等,所以CP的上下电流相等,从而VCO控制电压VCTRL保持恒定不变,环路锁定。

由于环路锁定时,FLL不工作,所以SSPLL的噪声模型可以简化成如图4所示的模型。与图2比较,很明显地看到少了分频器模块对系统的影响,使得锁相环的带内噪声大幅度减小。从而SSPD/CP对整个环路贡献的噪声为:

但是,参考信号源的噪声依然会被放大N2倍,所以在SSPLL中,带内噪声主要由参考信号源的噪声贡献。 3电路各模块设计与实现3.1压控振荡器

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选项替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

提出一种应用于10位逐次逼近型模数转换器(SAR ADC)的高精度比较器,具有精度高、功耗低的特点。该比较器采用差分结构的前置放大电路,提高输入信号的精度,其自身隔离效果减小了锁存器的回踢噪声和失调电压。动态锁存电路采用两级正反馈,有效提高比较器的响应速度。

输出缓冲级电路增强输出级的驱动能力,调整输出波形。该比较器电路采用SMIC 65 nm CMOS工艺技术实现,使用Cadence公司Spectre系列软件对进行仿真,设置工作电压2.5 V,采样频率2 MHz,仿真结果表明,比较器的分辨率是0.542 5 mV,精度达到11位,失调电压为1.405 μV,静态功耗为63 μW,已成功应用于10位SAR ADC。

0引言 随着集成电路的发展,数字通信得到了广泛应用,模数转换器(AnalogtoDigital Converter, ADC)作为实现模数转换的关键器件,得到了快速发展。在诸多不同结构的ADC类型中,逐次逼近型ADC(Successive Approximation AnalogtoDigital Converter, SAR ADC)具有面积小、功耗低、精度相对较高、输出数据无延迟的特点,广泛应用在消费电子、医疗设备、工业控制等诸多领域。而高精度比较器作为高性能SAR ADC的核心器件,其精度对ADC的性能起着至关重要的作用。因此,要实现高性能ADC,比较器的精度是关键。

当前对比较器的研究主要包括多级开环比较器、开关电容比较器、动态锁存再生比较器等。多级开环比较器具有较高的速度和精度,但是由于受到多级放大器的带宽限制,速度难以提升;开关电容比较器可以采用失调消除技术消除失调电压,提高精度,但是存在较为严重的电荷注入和时钟馈通效应,增加了设计难度;动态锁存比较器的响应速度快,但是回踢噪声和失调电压都比较大,不适用于高精度系统。因此,本文提出一种应用于10位SAR ADC的高精度比较器,采用前置差分预放大电路、两级正反馈Latch锁存判断电路和输出缓冲电路的结构,工作在2 MHz时钟频率下,失调电压低、回踢噪声小,精度达到11位,具有高精度、低功耗的特点,可以实现10位高性能SAR ADC的模数转换。

1比较器结构的选取 比较器主要分为放大器结构的静态比较器和通过时钟触发工作的动态比较器。前者主要用于传统的连续时间电路,而后者广泛应用于开关电容电路。忽略漏电流的因素,动态比较器由于速度快、静态功耗几乎为零,多用于ADC系统中。然而,动态比较器由于较大的失调电压和回踢噪声,限制了分辨率的提高。 Latch锁存器作为动态比较器中的重要组成部分,沟道长度越短,输入信号越大,锁存器响应越快。因此,为了提高响应速度,在锁存器前,前置一级差分放大电路,预先放大待比较信号,能够提高Latch的响应速度。

同时,差分结构可以去除误差信号成分,有效减少由直流失调电压、开关的时钟馈通效应、电荷注入效应而引起的误差。由于预放大电路内部和输出端加载隔离电路,使得其输出信号多次衰减后到达信号的输入端,能够有效减小回踢噪声对预放大电路输入端信号的影响。预放大锁存器的失调电压与正反馈锁存器相比较,有实质性降低。正反馈锁存器的失调电压通过预放大级,对输入管的贡献大幅度下降。因此,预放大锁存器的失调电压主要取决于预放大电路的失调。 一般传统的放大器的单位增益带宽为常数。

为了满足高精度的要求,前置预放大器的设计原则是高增益小带宽,然而过高的精度会降低比较器的速度。因此,要为前置预放大电路选取合适的增益。 综上所述,如图1所示,Vip和Vin分别是差分对的两个输入信号,采用前置差分预放大电路作为比较器信号输入端,兼顾精度和速度的要求,其隔离电路减小了Latch正反馈产生的回踢噪声以及失调电压;Δu1和Δu2作为锁存电路的输入,Latch锁存电路采用二级正反馈来提高比较器的响应速度,小尺寸的MOS管可以减小传输延时;锁存器输出的高低电平VA和VB输入给缓冲级,输出级采用反相器级联,调整波形,减小延时,增加驱动能力,最终输出Vout1和Vout2两个高低电平。

2比较器具体电路设计2.1前置差分预放大电路 比较器的第一级采用的是前置差分预放大电路,如图2所示。NMOS管M1和M2分别作为差分放大器的信号输入端,Vip和Vin是两个待比较的输入信号。晶体管M15、M17和M21具有复位功能,当时钟信号为低电平时,将当前输出清为零。PMOS管M16和M18充当滤波电容,提高预放大电路的精度。尾电流由开关信号控制,当开关信号为低电平时,尾电流被关闭,比较器处于低功耗模式。

预放大器电路通过放大两个差分输入信号Vip和Vin,从而提高比较器的精度,降低比较器的设计难度。PMOS管M5和M6组成PMOS锁存电路。这是因为比较器需要具有锁存功能的放大电路。当信号输入,经过前置差分放大器的放大后,输入信号被锁存,并成为输出结果。此时,下一级的锁存电路不工作。

在时钟信号的作用下,前置差分放大器停止工作,下一级的锁存电路在接收到上一级放大电路的输出结果后开始工作,并最终输出结果。 该前置放大电路有两条反馈路径。第一条反馈路径是晶体管M1和M2形成的电流负反馈。第二条反馈是晶体管M5、M6的栅漏极连接的电压正反馈。当正反馈系数小于负反馈系数时,整个电路将呈现负反馈,同时也失去了迟滞效应(如果实现反馈补偿,则成为传统的运算放大器)。

否则,整个电路会呈现正反馈,产生迟滞效应,能够有效地过滤掉输入噪声。这时: 如果β5/β3<1,则传输函数中没有延时; 如果β5/β3>1,则迟滞出现。

其中,β=(W/L)·K_(n·p)。

通过设置M3的宽长比大于M5,将该结构作为比较器的输入级,起放大作用,而非迟滞作用。

为了减少比较器设计的难度,在预放大级必须有一个大的增益。但是宽的带宽和大的增益是矛盾的,它们之间必须有一个折衷。

前置放大器级的增益可以表示为:

A=-gmM1R=-gmM1(gmM3-gmM5)(1)

单位增益带宽表示为:

GBW=gmM1/C(2)

gmM1,gmM3,gmM5分别是晶体管M1、M3和M5的跨导,C是前置差分放大电路的等效输出电容。由方程(1)、(2)可知,通过调整M1和M2的器件尺寸,可以使前置放大器获得适当的增益和带宽。

2.2两级正反馈锁存电路

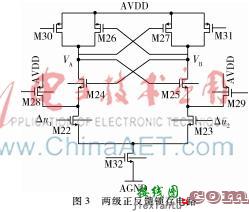

比较器的第二级采用的是两级正反馈Latch锁存电路,如图3所示。PMOS管M26和M27构成PMOS锁存器,NMOS管M24和M25构成NMOS锁存器。两级锁存加速了正反馈响应,使得输入信号Δu1和Δu2快速进行比较,形成高、低水平输出。 锁存阶段有两种工作模式,分别是复位和再生。

在复位模式,尾电流源M32关闭以降低功耗,此时开关M30和M31导通,使锁存器输出VA、VB两个高电平。开关M28和M29导通,使上一次输出迅速复位,准备接下来的比较。在再生模式,开关M30、M31、M28和M29都截止。M26和M27的漏极电压拉至电源电压AVDD,加大锁存器中的电流差,并且提高增益。通过两个正反馈回路,输入的电压差Δu1和Δu2进行迅速比较,比较结果保持在锁存器中,直到重新开始复位模式。

在这个设计中,两个正反馈回路的结构,使锁存阶段有较大的增益、更快的再生和复位速度。锁存器的常数时间主要取决于通道长度。因此,采用了两对小尺寸的交叉耦合晶体管。通过调整输入对管的宽度,以确保载流子的流动性。增加晶体管M22、M23的宽长比,这样在再生模式,就会有足够的电流来驱动锁存器迅速建立,减少响应时间。 2.3输出缓冲级电路

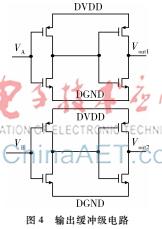

图4输出缓冲级电路比较器的第三级是输出缓冲级电路,如图4所示。输出缓冲级电路将锁存器输出的高低电平转换成逻辑电平,用于匹配数字电路。输出缓冲级由两级反相器组成。由于前一级输出电平未达到标准电平或波形不理想,两个反相器级联可以用于波形整形。同时增加了驱动能力,并降低了传输延迟。

3电路仿真与分析 在SMIC 65 nm CMOS工艺下,设置电源电压为2.5 V,采样率为2 MHz,使用Cadence公司Spectre系列软件对设计的电路进行仿真。 3.1前置差分预放大电路仿真

图5是前置差分放大器的频率特性曲线。设置共模电平为1.25 V,输入差分信号分别为0.5 V和 -0.5 V。仿真结果表明,前置放大器的电压增益为19.55 dB,-3 dB带宽约738.9 MHz。

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选项替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

相关文章

发表评论