本文介绍的是一款高性能的视频采集电路。该系统选用的视频解码器为Philip公司的高性能视频A/D转换器SAA7111.该器件是一款广泛应用于桌...

基于Video Port的Camera Link的图像采集接口设计

图像采集的运用非常广泛,经过几十年的发展,采集技术有了很大程度的进步。目前的专业采集设备集成度更高,分辨率更大,传输速度更快,针对性更强。

本文以DALSA公司的Spyder2系列线扫描相机为图像采集源,以TI公司的TMS320DM642多媒体处理器为核心,实现高速图像的采集和处理任务。

Spyder2线扫描相机以其高速的采集速度和先进的Camera Link接口,已广泛应用于工业生产线等领域。本方案集合了Camera Link和TMS320DM642的优点,缩短了设计周期,降低了难度,提高了设计的效率和设计质量。

1总体概述

Camera Link 是一种基于视频应用发展而来的通信接口标准,Camera Link接口采用National Semiconductor公司的Channel Link技术,其最高速率可达2.38Gbps。Camera Link相机和图像采集设备之间采用LVDS信号传输,从而简化了图像采集设备和模拟摄像头之间所必需的视频编解码等步骤,降低了生产成本和维护费用。

TMS320DM642作为多媒体处理器,内置3个专用的视频数据接口(Video Port)。每一视频接口有20位数据总线,可以在8位、10位、16位总线方式下进行视频采集或视频显示。采集频率最高可达80MHz。

DALSA Spyder2相机采用单通道Channel Link输出,每线输出2048像素,每个像素8位。为了图像处理的方便,采集接口将视频数据重整为完整帧并缓存于SDRAM中。TMS320DM642的Video Port接口设置为8位的RAW Data采集模式。总体结构如图1所示。DALSA Spyder2相机采集到的视频信号通过Video Port 0传输到SDRAM中缓存,DM642再通过EMIFA从SDRAM中读取每帧图像进行分析处理。

图1总体结构图

2关键硬件设计

2.1视频解串电路

Camera Link标准中,相机的信号被分为3种:视频数据信号、相机控制信号、串行通信信号。

视频解码部分采用National Semiconducor公司TSSOP56封装的DS90CR288A接收器来完成,它能够将4路LVDS串行数据流转换为2位并行TTL/CMOS数据,在传输时钟CLK的每个周期,将28位并行数据输出。

DS90CR288A解码出的TTL/CMOS信号可以分成2类:图像信号和图像时钟信号(WCLK)。其中图像信号又由24位图像数据信号和4位图像同步信号组成,这些信号都符合Channel Link技术标准。

图像同步信号包括:FVAL(Frame Valid)、LVAL(Line Valid)、DVAL(Data Valid),分别为帧有效信号、行有效信号和数据有效信号。当FVAL、LVAL、DVAL同时有效(为高电平时),表示相机正在输出有效的图像数据。Channel Link的图像同步信号和时钟信号的关系如图2所示。

图2视频同步信号时序图

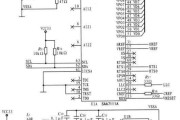

DALSA Spyder2 相机为线扫描数字摄像机,设置为8位灰度输出,相机在每个时钟的上升沿传送串行图像信号,FVAL、DVAL信号厂商固定为高电平,只由LVAL信号控制相机的图像输出。针对这一特性,设计充分利用TMS320DM642的视频接口这一优势,由图像时钟(WCLK)来控制视频口的采集时钟(VP0_CLK0),相机的行有效信号(LVAL)控制视频口的采集使能端(VP0_CTL0),图像信号D[7..0]送往Video Port的数据总线VP0D[9..2]。采集接口与TMS320DM642的视频口连接原理图如图3所示。

图3Camera与TMS320DM642接口示意图

当相机输出一行有效图像数据时,TMS320DM642的视频口在图像时钟的上升沿将解串的图像信号采集到视频口的内部高速FIFO中。当内部FIFO缓存超过编程门限(threshold)后将自动触发一个专用EMDA通道将FIFO中的图像数据搬移到SDRAM中。整个视频的采集过程都没有DSP干预,避免了由于数据搬运而引发的错误同时减少了数据传输的系统资源开销。

2.2相机控制电路

Camera Link标准中规定了4位相机控制信号:CC1、CC2、CC3和CC4,需要一个4位的LVDS驱动器,DALSA Spyder2 相机遵循Camera Link标准采用了CC1、CC2、CC3三个相机控制位,分别完成外部同步控制、像素重置控制和采集方向控制,CC4控制位暂时闲置。采用National Semiconducor公司的DS90LV047A芯片来驱动这4位相机控制信号,如图4所示。

图4相机控制电路示意图

DS90LV047A将CPLD发送过来的外部控制信号转化为符合LVDS标准的控制信号。相机控制信号的使用是可选择的,像DALSA Spyder2系列,没有控制信号的参与也能完成采集。

2.3相机通信电路

DALSA Spyder2相机需要一组由9600bps、一个开始位、一个结束位、无校验位组成的串行异步信号(±SerTFG、±SerTC)来进行相机参数的设置和信息反馈。本设计选用了National Semiconducor公司的DS90LV019集成驱动器/接收器来进行TTL/LVDS转换,如图5所示。

图5相机通信电路示意图

DS90LV019有4种工作模式,模式的选择由DE和/RE两个信号的状态决定。当DE和/RE都为高时,IC工作在驱动模式;当DE和/RE都为低时,IC工作于接收模式;当DE为低,/RE为高时,IC工作在三态模式;当DE为高,/RE为低时,IC工作在全双工模式。这里采用一片DS90LV019作为串行通信LVDS信号的收发器,工作于全双工模式。再用Maxim公司的MAX3221来进行TTL/RS232电平间的转换。控制端通过RS232接口发送的相机命令再通过DS90LV019传送给相机,相机接收后给出的反馈信息再通过DS90LV019和MAX3221传送给控制端。

3软件设计

DDK是TI公司用来简化设备驱动程序开发的软件套件,它提供了一些外设的完全驱动函数,其中就有Video Port专用的Minidriver驱动程序库。

视频驱动程序主要包括微驱动、类驱动和中间接口3个方面的设计。视频采集驱动程序中,在GIO类驱动程序的基础上进一步封装成FVID类。将微驱动细分为视频端口类和制定的编解码芯片微驱动,两者之间通过外部设备控制接口EDC实现对外围芯片的打开、控制和关闭等操作。

为了实现Camera Link相机图像数据的采集,TMS320DM642的视频口必须被配置为RAW DATA采集方式。与通常的BT.656采集方式不同,当Video Port工作于RAW DATA采集方式下,TMS320DM642不会进行数据选择和数据判断,而BT.656方式需要判断SAV/EAV同步码,RAW DATA采集方式主要用于从ADC获取原始的图像数据。

在RAW DATA采集方式下,当CAPEN信号(VP0_CTL0)被使能时,Video Port开始采集VP0D数据线上的数据,采样数据的大小可以通过VCxSTOP1的VCXSTOP和VCYSTOP位进行设置,通过VCXSTOP和VCYSTOP的组合,TMS320DM642允许单帧最多采集4096Kb个采样数据。当采集数据达到VCXSTOP和VCYSTOP所设置的值的时候,采样完成,此后,CAPEN信号必须保持至少2个时钟周期的无效状态。系统中设置采集帧大小为2048pix×256pix,及采集524288个数据后打包为一帧,系统采用相机的时钟WCLK=25ns,行有效周期LVAL=50μs,行无效周期为150μs,150μs>>25ns,能保证CAPEN至少2个时钟周期无效状态的要求。

帧同步处理对于RAW DATA方式的图像采集是一个很关键的因素。由于RAW DATA采集方式的数据不包含任何类似于BT.656数据流那样的帧启/停标识码(SAV/EAV CODE),也不提供外部的水平和垂直同步信号,帧同步时无法实现的,所以DDK自带的Minidriver驱动程序无法完成RAW DATA方式的图像采集,则需要对Minidriver驱动进行修改来实现RAW DATA采集,通过设置Video Port的第一场采样开始寄存器VCxSTRT1,并增加采样垂直消隐间隔VCVBLNKP和开始同步使能位SSE来间接的实现帧同步功能。修改后的视频采集结构为:

typedef struct {

Int cmode;//采集模式选择

Int fldOp;//场/帧操作

/*8~15位*/

Int scale;//1/2缩放使能

Int resmpl;//灰度采集使能

Int bpk10Bit;//10位采集模式

/*16~23位*/

Int hCtRst;//水平计数复位模式

Int vCtRst;//垂直计数复位模式

Int fldDect;

Int extCtl;//使能外部时钟控制

Int fldInv;//使能场反转

/*原始模式采集参数*/

Uint16 sse;//开始同步使能位

Uint16 vcvblnkp;//垂直消隐间隔

Uint16 sse; //开始同步使能位

Uint16 vcvblnkp; //垂直消隐间隔

Uint16 fldXStrt1; //场1 X开始

Uint16 fldYStrt1; //场1 Y开始

Uint16 fldXStrt2; //场2 X开始

Uint16 fldYStrt2; //场2 Y开始

Uint16 fldXStop1; //场1 X停止

Uint16 fldYStop1; //场1 Y停止

Uint16 fldXStop2; //场2 X停止

Uint16 fldYStop2; //场2 Y停止

Uint16 thrld;//视频FIFO阈值

/*帧缓存设定*/

Int numFrmBufs; //缓存帧数

Int alignment;//帧缓存对齐方式

Int segId;//存储分配ID

/*EDMA优先等级*/

Int edmaPri;//EDMA通道优先级

Int irqId;

} VPORTCAP_Params;

当SSE位被置位且视频口采样使能信号有效,在2个垂直消隐间隔以后,视频口开始采集数据。通过设置VCVBLNKP位,可以定义一个垂直消隐信号时间的长度。为了保证能在一帧数据开始的时候同步,系统将VCVBLNKP置位为0。

此外,系统采用的是DS90CR288A相机解码芯片,不同于DDK中使用的SAA7121解码芯片,所以在相机的接口配置中(VPORT_PortParams)需要对EDC接口进行修改。

DS90CR288A主要包括打开和关闭两个操作,可以通过对外部CPLD中的相机控制寄存器VIDEO_CLR置位来操作。修改得到的EDC控制函数如下:

static EDC_Handle Camera_open(String devName, Arg optArg){

Int devId;

if(devName[0] != '/') {

devId = -1;//无效端口

} else if(devName[1] == '0') {

devId = 0;

VIDEO_CLR = 0x1;//0号端口,寄存器置高,使能解码

} else if(devName[1] == '1'){

devId = 1;

VIDEO_CLR = 0x1;//1号端口,寄存器置高,使能解码

} else {

devId = -1;//无效端口

}

return (EDC_Handle)devId;

}

static Int Camera_close(EDC_Handle handle){

VIDEO_CLR = 0x0;//寄存器置低,停止解码

return EDC_SUCCESS;

}

4结论

本设计实现了TMS320DM642通过Video Port与Camera Link相机的无缝连接,硬件接口设计简单,系统编程也很方便。整个图像的采集都不用CPU的参与,可以提高整个系统的工作效率。

标签: Camera link TMS320DM642 视频接口 视频采集

相关文章

发表评论