该图为LatticeECP3设计的视频协议板电路图。 LatticeECP3 FPGA系列能提供高性能的特性如增强的DSP架构,高速SERDE...

解读FPGA电容在线测试系统电路设计方案

PCB在焊接完成后,需要对其元器件进行测试,传统的方法是将其焊离PCB板后测试,但该方法不仅 麻烦、效率低,并且容易损伤电路板而极不实用;另一方法就是人工结合机器进行测试,但这需要测试人员有一定的经验,也给测试带来了一定的不确定性,使得测 试结果的精准度无法达到现代电路板的可靠性要求。所以,本文研究了一种可行的、简单实用及高精度的电容在线测试电路。另外,随着EDA技术的快速发 展,FPGA以其高集成度、高可靠性及灵活性等特点正在快速成为数字系统开发平台,在多种领域都有非常广阔的应用前景。本设计结合上述两特点,设计了一种 基于向FPGA内植入Nios II嵌入式软核作为控制器的电容在线测试电路。

测试原理

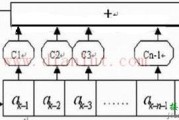

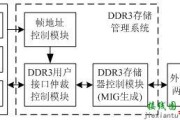

在线测试的基本思想是应用电气隔离技术,将被测元器件在电气上和与其相连的元件隔离,进而一一检测PCB板上的每一个元件。隔离方法如图1所示。设待测元件为Zx,周围与之相连的元件阻抗等效为Z1、Z2,并将其另一端与测试电路同地。因为运 放正向输入端接地,根据“虚地”原则,Z2两端等电位,都为地,即Z2被隔离;另外Vi为理想电压源时,内阻为零,Z1可视为电压源的输出负载,不影响 Zx上电压降,即Z1也被隔离。可见,只要确定输入,测得输出结果,就可计算出被测元件的大小。

信号源电路

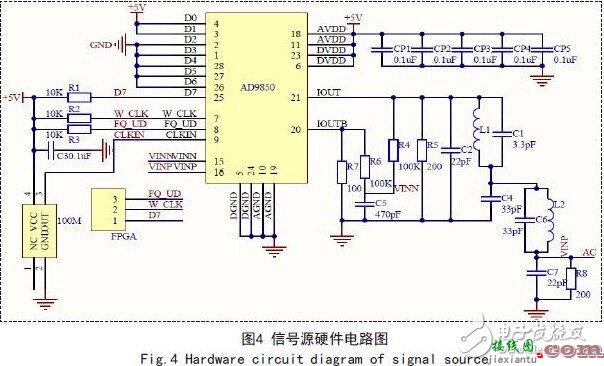

串行输入方式,在W_CLK上升沿把数据位D7的一位数据串行输入,当输入40位后,用一个FQ_UD脉冲即可更新输出频率和相位。图4为DDS硬件电路图。

其中,D0~D7为八位数据输入端口,给内部寄存器装入40位控制数据,本文采用串行输入,所以只 用到D7位与FPGA相连;CLKIN为外部参考时钟输入,本设计采用100M外部时钟输入;W_CLK为字输入信号,上升沿有效;FQ_UD为频率更新 控制信号,时钟上升沿确认输入数据有效;VINP和VINN分别为内部比较器的正负输入端;IOUT为内部DAC输出端;IOUTB为“互补”DAC输出 端;AVDD和DVDD采用+5V供电。IOUT输出信号经过滤波器后作为测试电路的激励信号。

通过上述实测值与标准值的比较可以看出本文设计的由FPGA控制的电容在线测试系统具有多量程自动选择,测试精度高,使用方便等特点,测试范围达到0.01μF~3μF.经理论分析和试验证明,该设计具有很强的实用性和可靠性。

相关文章

发表评论