DRV2605($1.8000 器件设计用于通过共享的I2C 兼容总线提供极为灵活的ERM 和LRA 传动器触控。该控制使得主机处理器不用再生成脉宽调...

IP模块与FX模块电路设计 - 以太网收发电路设计方案详解

复位时,IP113首先读取93C46的00H中的内容,只有00H[15:0]=55AAH时,才会继续从EEPROM中读取参数,否则以缺省值或特定的管脚电平值设置工作寄存器。01H中的值设置LED输出控制寄存器,控制两个LED矩阵的亮、灭和闪烁,以分别显示两个端口的连接、活动、全/半双工和速率(10Mbps/100Mbps)。02H中的值设置交换控制寄存器1,选择系统的流控制方式和冲突保护。03H中的值设置交换控制寄存器2,控制系统的丢包、地址失效、优先级和算法补偿。04H中的值设置收发器控制寄存器,其中04H[13:11]的5 种取值:000、100、101、110和111,分别对应收发器的5种工作状态:NWAY、10Mbps(半双工)、10Mbps(全、半双工)、 100Mbps(半双工)和100Mbps(全、半双工)。05H~0AH中的值分别设置收发器确认寄存器、测试寄存器和验证方式寄存器。

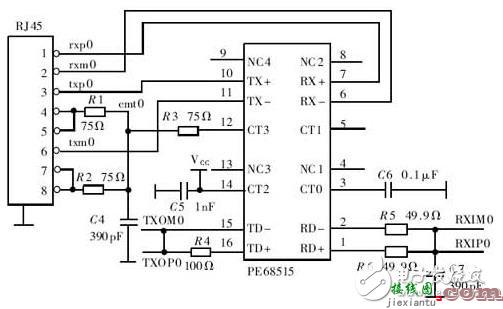

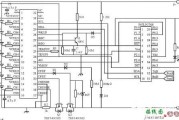

Port1的TXOP和TXOM是TP发射数据对,RXIP和RXIM是TP接收数据对。图4的TP模块电路中,RJ45接口将MLT-3码流以太网信号经过耦合脉冲变压器PE68515变为单极性信号。

图4 IP模块电路图

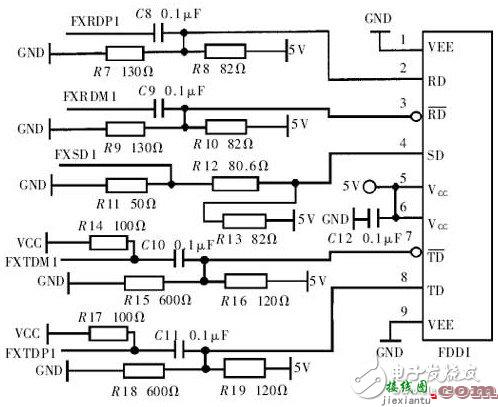

Port2的FXRDP和FXRDM是FX的接收数据对,FXTDP和FXTDM是FX的发射数据对。FXSD是光电检测信号,当接收到的光信号经光电转换后电平低于1.2V时,FXSD输出连续的PECL电平。图5是FX模块的电路图,电路中采用标准的FDDI数据接口。由于调制驱动和接收解调电路采用5V电源,而系统其它部分均使用2.5V电源,FDDI中的信号均是PECL电平,因此必须经电平转换(如图5所示),才能把这两部分联系起来。

图5 FX模块电路图

----------------------------------------

智能家电技术资料集锦——让家电设计迈入崭新时代!

相关文章

发表评论