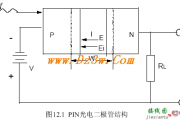

PIN光电二极管是在PN结的P型层和N型层之间夹了一层本征半导体(semiconductor ,形成P-I-N结构而得名,如下图所示:如上图所示,处于...

用可编程逻辑器件设计组合逻辑电路

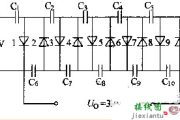

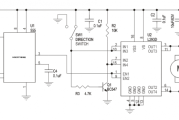

可编程逻辑器件的基本电路—可编程二极管与门电路和可编程二极管或门电路已介绍。而按PLD所包含门多少(即密度高低)分:低密度PLD器件—等效逻辑门﹤1000个;高密度PLD器件—等效逻辑门成千上万(几千、几万、几十万门以上);这里讨论低密度器件。图示电路是低密度PLD的结构图:

输入电路由输入缓冲器构成,“与”阵和“或”列阵是低密度PLD的核心电路,输出电路主要由三态输出门和异或门组成。按“与”阵和“或”阵的可编程或者不可编程分,低密度PLD有下面的种类:

1)只读存储器---ROM,PROM(Programmable Read Only Memory)

2)现场可编程逻辑阵列---FPLA,FPLA(Field Programmable Logic Arrays)

3)可编程阵列逻辑---PAL,PAL(Programmable Arrays Logic)

4)通用阵列逻辑---GAL,GAL(Generic Array Logic)

它们的结构特性如表所示:

这些PLD器件在实现各种组合逻辑电路时,各有优点。

二、组合型可编程阵列逻辑(PAL)结构

由于PAL的与阵可编程,或阵为不可编程的固定连接,所以非常适合于产生各种组合逻辑函数。它的输出电路结构又有三种。

⑴ 低电平输出的固定结构:

⑵ 可编程I/O结构:

这种电路结构,其输出可作输出端用,也可作输入端用,由G3门决定,而G3门输出由输入项编程来确定。如G3门输出高电平时,三态门G1为工作态,I/O端作输出端用,输出结果由编程而定;G3门输出低电平时,G1输出高阻态,I/O端作输入端用。

⑶ 可编程极性输出结构:

当异或门的输入熔丝熔断时,输出 ,低输出有效;当熔丝短路时,

,低输出有效;当熔丝短路时, ,高输出有效。熔丝的通断由一个可骗程乘积项的输出控制。

,高输出有效。熔丝的通断由一个可骗程乘积项的输出控制。

三、可编程逻辑器件的应用

可编程逻辑器件(PLD)的应用需要开发软件的支持,这是与普通数字集成电路完全不一样的地方。开发软件的种类非常多,往往某个公司生产的PLD器件,该公司都有相应的开发软件。低密度PLD器件的开发软件主要有:PALSIM、FM、CUPL、PLDesigners、ABEL等。

在电子技术实验课中将简单介绍ABEL语言,并用ABEL语言进行数字电路的设计和仿真。开发低密度PLD器件的过程:

1)在PLD开发环境下进行逻辑功能描述,(用硬件描述语言或原理图等方法);

2)在LPD开发环境下编译、仿真逻辑功能描述,检验逻辑功能的正确性;

3)在PLD开发环境下适配逻辑功能的描述,并将逻辑描述映射到具体的PLD器件中,得到编程所需的JEDEC文件;

4)连接PC机与编程器,把JEDEC文件下载到PLD器件中;

5)将下载后的PLD器件接上电源、输入数据、控制信号等,校验逻辑功能是否满足设计要求。

应用PLD器件的主要工作是1)和5),其它都由开发软件完成。

相关文章

发表评论